# Linear Integrated Circuits Laboratory Manual

| Name | : |  |  |  |  |  |

|------|---|--|--|--|--|--|

|      |   |  |  |  |  |  |

|      |   |  |  |  |  |  |

|      |   |  |  |  |  |  |

Dr. S.B. Bhanu Prashanth

Professor

Department of Medical Electronics

B.M.S. College of Engineering

Bengaluru 560 019

2021

USN:

# **CONTENTS**

| Sl.<br>No. | Particulars                                        | Page<br>No. |

|------------|----------------------------------------------------|-------------|

| 1.         | Basic Op-Amp Applications                          | 3           |

| 2.         | Voltage to Current Converter                       | 9           |

| 3.         | Instrumentation Amplifier                          | 12          |

| 4.         | Wein Bridge and RC Phase-shift Oscillators         | 16          |

| 5.         | ZCD & Voltage Level detectors                      | 20          |

| 6.         | Schmitt Trigger Circuit                            | 24          |

| 7.         | Precision HW and FW Rectifiers.                    | 28          |

| 8.         | First & Second order Active Low Pass Filters       | 33          |

| 9.         | First & Second order Active High Pass Filters      | 38          |

| 10.        | Astable and Monostable multivibrators using IC 555 | 43          |

| 11.        | DAC using R-2R ladder network                      | 50          |

Get the facts, **or** the facts will get you.

And when you get them, get them right.

**Or** they will get you wrong.

- Thomas Fuller

#### **EXPERIMENT NO. 1**

#### Date:-

# **BASIC OP-AMP APPLICATIONS**

**Aim:** To design and study the basic applications of Op-amp as amplifiers and Summing Amplifiers.

#### Apparatus Required:

| Sl. | Particulars                | Range           | Quantity |

|-----|----------------------------|-----------------|----------|

| No. |                            |                 |          |

| 1   | Op-amp                     | μΑ 741          | 2        |

| 2.  | Resistors                  | 1K, 10K         | 2 each   |

| 3.  | Base board (IC and Spring) |                 | 1 each   |

| 4.  | Adopters                   |                 | 2        |

| 5.  | DMM and Probes             |                 | 1+2 set  |

| 6.  | Connecting wires           |                 |          |

| 7.  | Power supply               | 0-5 V & + /-15V | 1        |

#### **Procedure:**

#### I. Amplifiers:

- 1. Connections are made as shown in the circuit diagram of figure (1).

- 2. Input voltage  $V_i$  is increased in steps of 0.1 V and at each step the output voltage  $V_o$  is noted down.

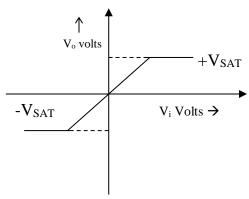

- 3. Readings are tabulated and a graph of V<sub>0</sub> Vs V<sub>i</sub> is plotted.

- 4. The input DC supply is replaced with an ASG and a sinusoidal input of adequate amplitude (to cause output saturation) @ a frequency of 1 KHz is applied. The input and output are simultaneously fed to a CRO and the transfer curve is observed and traced.

- 5. The above procedure is repeated for circuit of figure (2).

# II. Adders/Subtractors :- [In Inverting and Non-inverting modes]

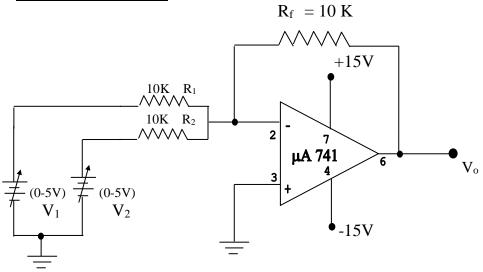

- 1. Connections are made as shown in the circuit diagram of figure (3).

- 2. Different input voltages  $(V_1 \text{ and } V_2)$  are applied and the output voltage is measured using a multimeter.

- 3. The readings are tabulated and the measured values are compared with the theoretical values.

- 4. The above procedure is repeated for circuits of figures (4), (5).

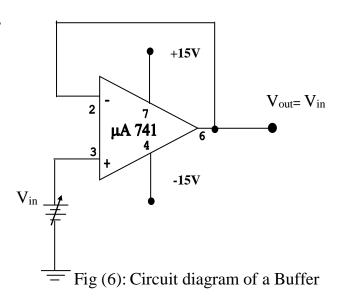

# III. Buffer/ Voltage Follower:-

- 1. Connections are made as shown in the circuit diagram of figure (6).

- 2. The input voltage is varied in steps and the output voltage is noted to be approximately equal to input.

#### Circuit diagrams and designs:-

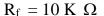

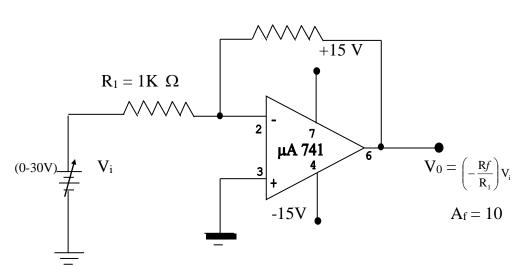

#### 1) <u>Inverting Amplifier</u>:-

Fig (1): Circuit diagram of an Inverting amplifier:

Design Example:

Let

$$|A_v|=10$$

. Choose  $~R_1=1~k\Omega$

$$|A_v|=\frac{R_{\rm \,f}}{R_{\rm \,1}}~~ \text{Therefore}~R_f=10~k\Omega$$

# **Tabular Column:-**

| Sl. | V <sub>i</sub> Volts | Vo (Theoretical) | Vo (Practical) |

|-----|----------------------|------------------|----------------|

| No. |                      | Volts            | Volts          |

|     |                      |                  |                |

|     |                      |                  |                |

|     |                      |                  |                |

|     |                      |                  |                |

|     |                      |                  |                |

|     |                      |                  |                |

|     |                      |                  |                |

|     |                      |                  |                |

|     |                      |                  |                |

|     |                      |                  |                |

|     |                      |                  |                |

|     |                      |                  |                |

|     |                      |                  |                |

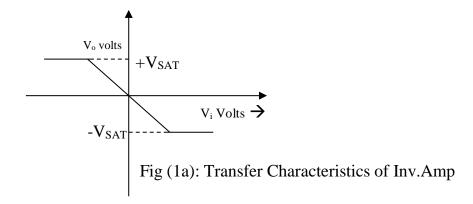

Fig (2): Circuit Diagram of a Non –inverting amplifier

# **Design Example:**

Let

$$|A_v| = \frac{R_f}{R_1} = 11$$

. Let  $R_1 = 1 \text{ K } \Omega$  .== >  $R_f = 10 \text{ k} \Omega$

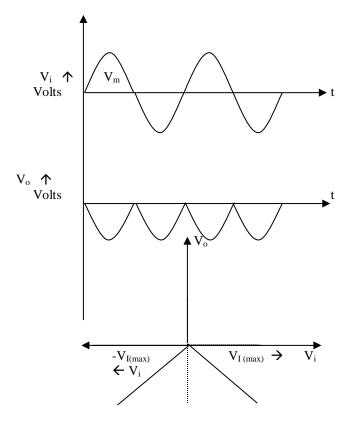

Fig (2a): Transfer Characteristics of Non-inv Amp

# Tabular Column :-

| Sl. | V <sub>i</sub> Volts | Vo (Theoretical) | Vo (Practical) |

|-----|----------------------|------------------|----------------|

| No. |                      |                  |                |

|     | 0.0                  |                  |                |

|     | 0.1                  |                  |                |

|     | 0.2                  |                  |                |

|     | -0.3                 |                  |                |

|     | -0.65                |                  |                |

|     | 3.0                  |                  |                |

|     | -3.0                 |                  |                |

\_\_\_\_\_\_

# 3) Inverting adder :-

Fig (3): Circuit diagram of an Inverting adder

$$\begin{aligned} \textbf{Design Example:} \quad & V_o = \text{-} \quad \left[ \frac{R_{\rm f}}{R_{\scriptscriptstyle 1}} \, V_{\scriptscriptstyle 1} + \frac{R_{\rm f}}{R_{\scriptscriptstyle 2}} \, V_{\scriptscriptstyle 2} \, \right] \\ & \text{If} \quad & R_f = R_1 = R_2 = 10 \, \, \text{K} \quad \text{. Then} \quad & V_0 = \text{-} \left[ V_1 + V_2 \right] \end{aligned}$$

#### Tabular Column :-

| Sl. | V <sub>1</sub> (volts) | V <sub>2</sub> (Volts) | V <sub>o</sub> (volts) |

|-----|------------------------|------------------------|------------------------|

| No. |                        |                        |                        |

|     |                        |                        |                        |

|     |                        |                        |                        |

|     |                        |                        |                        |

|     |                        |                        |                        |

|     |                        |                        |                        |

|     |                        |                        |                        |

|     |                        |                        |                        |

|     |                        |                        |                        |

|     |                        |                        |                        |

------

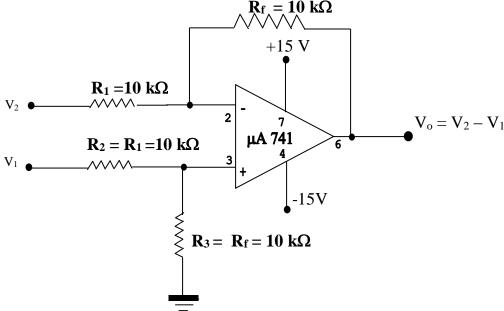

# 5) Differential Amplifier as Subtractor ;-

Fig (5): Circuit Diagram of Subtractor (Differential Amplifier)

# **Design Example:-**

$$\mathbf{V_o} = -\frac{R_f}{R_1} (V_2 - V_1)$$

$R_1 = R_2 = R_f = 10 \text{ k } \Omega \implies V_o = [V_1 - V_2]$

# Tabular Column :-

| S1. | $V_1$ | V <sub>2</sub> | Vo(practical)<br>Volts | V <sub>o</sub> (theoritical) |

|-----|-------|----------------|------------------------|------------------------------|

| No. | Volts | Volts          | Volts                  | Volts                        |

|     |       |                |                        |                              |

|     |       |                |                        |                              |

|     |       |                |                        |                              |

|     |       |                |                        |                              |

|     |       |                |                        |                              |

|     |       |                |                        |                              |

|     |       |                |                        |                              |

|     |       |                |                        |                              |

|     |       |                |                        |                              |

|     |       |                |                        |                              |

|     |       |                |                        |                              |

|     | 1     |                |                        |                              |

# 6) Buffer/Voltage Follower ;-

# **TABULAR COLUMN:-**

| $V_{in}$ Volts | Vout Volts            |

|----------------|-----------------------|

|                |                       |

|                |                       |

|                |                       |

|                |                       |

|                |                       |

|                |                       |

|                |                       |

|                |                       |

|                | V <sub>in</sub> Volts |

#### Experiment No. 2

#### Date:

#### **VOLTAGE TO CURRENT CONVERTER**

AIM: To design and test I to V and V to I converters for the given specifications.

#### APPARATUS REQUIRED:

| Sl.<br>No. | Particulars           | Range        | Quantity |

|------------|-----------------------|--------------|----------|

| 1          | IC μA 741             |              | 1        |

| 2          | Milli ammeters        | 0-100 mA     | 1        |

|            |                       | 0-50 mA      | 1        |

|            |                       | 0-10 mA      | 1        |

| 3          | Power supply          | 0-30 volts   | 1        |

| 4.         | Power supply          | +15 / -15 V  | 1        |

| 5.         | Resistors             | $470~\Omega$ | 2        |

|            |                       | 1 k Ω        | 2        |

| 6          | IC base board         |              | 1        |

|            | Base board            |              | 1        |

| 7          | Multimeter and probes |              | 1 set    |

| 8          | Connecting wires      |              |          |

#### **PROCEDURE:**-

#### **I. Voltage to Current converter:-**

- 1. The connections are made as shown in the circuit of figure (1).

- 2. The load resistor  $R_L$  a constant value (say  $R_L = 200 \Omega$ )

- 3. The input voltage  $V_i$  is varied in steps and corresponding values of  $I_f$  are noted. The theoretical values of  $I_f$  are computed and compared.

- 4. All the readings are tabulated in table (1).

- 5. The i/p voltage  $V_i$  is kept at a constant value ( at 2 Volts ) and the load resistance is varied from around 50 ohms to 10 kohms and at each step the corresponding values of  $I_L \& V_L$  are noted down and recorded in table (2).

- 6. The above procedure is repeated for circuit of figure (2). The readings are tabulated in tables (3) and (4).

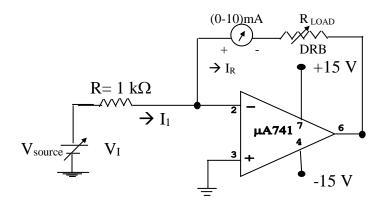

Fig (1): V TO I CONVERTERS FOR FLOATING LOAD

**Design Example:**  $I_1 = I_R = \frac{V_i}{R}$  because of virtual ground .

Therefore

$$I_L = \frac{1}{R} V_I$$

Here  $I_L$  is independent of  $R_{LOAD}$  within specified limits.

Choose  $R = 1 k \Omega$

Therefore  $I_L = (\ 10^{\ -3}\ V_I\ )$  Amperes. Where  $V_I$  is in volts.

# Tabular Column (1):-

# Tabular Column (2):-

For  $R_L = 200 \Omega$  constant

| 1 of 1th 200 12 constant |                            |                              |  |  |  |

|--------------------------|----------------------------|------------------------------|--|--|--|

| Vi                       | I <sub>L</sub> (Practical) | I <sub>L</sub> (Theoretical) |  |  |  |

| Volts                    |                            |                              |  |  |  |

|                          |                            |                              |  |  |  |

|                          |                            |                              |  |  |  |

|                          |                            |                              |  |  |  |

|                          |                            |                              |  |  |  |

|                          |                            |                              |  |  |  |

|                          |                            |                              |  |  |  |

|                          |                            |                              |  |  |  |

|                          |                            |                              |  |  |  |

| $V_i = 2 V constant$ |          |  |  |  |

|----------------------|----------|--|--|--|

| $R_{\rm L}$          | $ m I_L$ |  |  |  |

|                      |          |  |  |  |

|                      |          |  |  |  |

|                      |          |  |  |  |

|                      |          |  |  |  |

|                      |          |  |  |  |

|                      |          |  |  |  |

|                      |          |  |  |  |

|                      |          |  |  |  |

|                      |          |  |  |  |

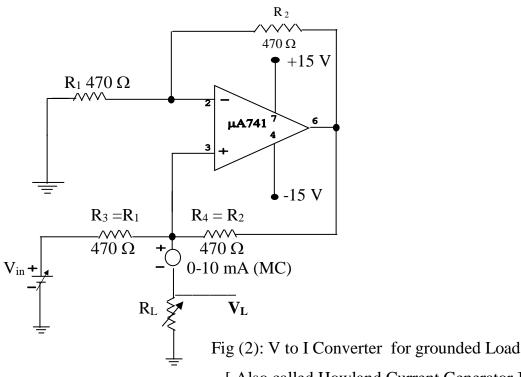

[ Also called Howland Current Generator ]

# **Design Example:**

$$I_o = \frac{1}{R_a} V_i$$

Let  $R_3 = 470 \Omega$

Then

$$I_o = 0.0021$$

$V_i$  volts  $I_o =$  Amps

# Tabular Column(3):-

# $R_L = 500 \Omega$ constant

| $\mathbf{R}_{\mathrm{L}}$ – . | Joo 22 Constant |                            |

|-------------------------------|-----------------|----------------------------|

| V <sub>i</sub> in             | $I_{L}$         | I <sub>L</sub> (Practical) |

| volts                         | (Theoretical)   |                            |

|                               |                 |                            |

|                               |                 |                            |

|                               |                 |                            |

|                               |                 |                            |

|                               |                 |                            |

|                               |                 |                            |

|                               |                 |                            |

|                               |                 |                            |

|                               |                 |                            |

# Tabular Column(4):-

$V_i = 5 \text{ volts (constant)}$

| ${ m I}_{ m L}$ | $V_{L}$        |

|-----------------|----------------|

|                 |                |

|                 |                |

|                 |                |

|                 |                |

|                 |                |

|                 | I <sub>L</sub> |

#### **Experiment No. 3** Date:

#### **INSTRUMENTATION AMPLIFIER**

<u>AIM</u>: To design and test an instrumentation amplifier for the given gain and to determine CMRR.

#### APPARATUS REQUIRED :

| Sl.<br>No. | Particulars           | Range       | Quantity |

|------------|-----------------------|-------------|----------|

| 1.         | ΙC μΑ 741             |             | 3        |

| 2.         | Resistors             | 10 k Ω      | 7        |

| 3.         | Power supply          | +15 / -15 V | 1        |

|            |                       | 0-30 volts  | 2        |

| 4.         | Multimeter and probes |             | 1 set    |

| 5.         | Connecting wires      |             | 1 set    |

| 6.         | IC base board         |             | 1        |

| 7.         | Base board            |             | 1        |

#### **PROCEDURE:**

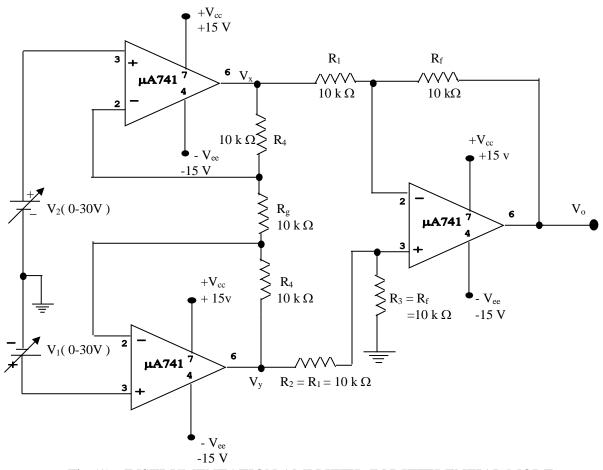

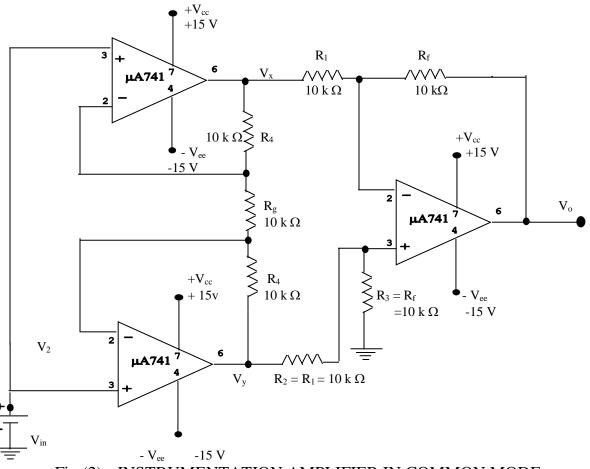

- 1. Circuit connections are made as shown in figure (1) for the differential mode.

- 2. Inputs  $V_1$  and  $V_2$  are varied in steps and  $V_0$  is measured using a Multimeter and tabulated.

- 3. The Differential gain is calculated and verified with the designed gain.

- 4. For the common mode, connections are made as per circuit diagram (2), and  $V_{\rm in}$  is varied in steps ( 2 V, 3V etc., ) .V<sub>o</sub> is measured using a multimeter and recorded at each step.

- 4. The Common mode gain is calculated and recorded.

- 5. The CMRR in calculated and recorded.

#### **CIRCUIT DIAGRAMS AND DESIGN:-**

Fig (1): INSTRUMENTATION AMPLIFIER IN DIFFERENTIAL MODE

# **Design Example:-**

$$V_{o} = -\frac{R_{f}}{R_{1}} \left[ 1 + \frac{2R_{4}}{R_{g}} \right] (V_{1} - V_{2})$$

$$A_{vf} = \frac{V_{o}}{V_{1} - V_{2}} = -\frac{R_{f}}{R_{1}} \left( 1 + \frac{2R_{4}}{R_{g}} \right)$$

For  $R_{f} = R_{1} = R_{4} = R_{g} = 10 \text{ K}\Omega$

$$V_{o} = -3 \quad (V_{1} - V_{2}) \quad i.e. \quad V_{o} = -3 \quad V_{d}$$

# Tabular Column (1):-

| V <sub>1</sub> in volts | V <sub>2</sub><br>in volts | V <sub>o</sub> (Theoretical) in volts | V <sub>o</sub><br>(measured)<br>in volts | $A_{d} = \frac{V_{o}}{V_{1} - V_{2}}$ diff. gain |

|-------------------------|----------------------------|---------------------------------------|------------------------------------------|--------------------------------------------------|

| 0.0                     | 0.5                        |                                       |                                          |                                                  |

| 1.5                     | 0.8                        |                                       |                                          |                                                  |

| 2.0                     | 2.6                        |                                       |                                          |                                                  |

| 2.2                     | 2.55                       |                                       |                                          |                                                  |

| 5.4                     | 4.4                        |                                       |                                          |                                                  |

| 2.2<br>5.4<br>6.4       | 7.4                        |                                       |                                          |                                                  |

| 4.6                     | 6.8                        |                                       |                                          |                                                  |

|                         |                            |                                       |                                          |                                                  |

Average  $A_d =$

------

Fig (2):- INSTRUMENTATION AMPLIFIER IN COMMON MODE

# **Tabular Column**

| Vin<br>in volts           | V <sub>o</sub> in volts | $A_{c} = \frac{V_{o}}{Vin}$ Common mode gain |

|---------------------------|-------------------------|----------------------------------------------|

| 2.0<br>3.0<br>5.6<br>12.0 |                         |                                              |

Average  $A_c =$

-----

CMRR =

$$20 \log \frac{A_d}{A_c}$$

----( in dBs)

**Results:-**

**Exercise :** Design and test an Instrumentation Amplifier for different gains like 30 and 100. Calculate the CMRR and comment on the results.

#### **Experiment No. 4**

Date:

#### WEIN BRIDGE AND RC PHASE-SHIFT OSCILLATORS.

AIM: To design and test Op-amp based Weinbridge and RC-Phase Shift Oscillators.

#### APPARATUS REQUIRED:

| Sl.<br>No. | Particulars           | Range           | Quantity |

|------------|-----------------------|-----------------|----------|

| 1.         | OP-Amp                | LM 741 or OP 07 | 1        |

| 2          | Resistors             |                 | 2        |

| 3.         | Capacitors            |                 | 2        |

| 4.         | Dual Power Supply     | + / -15 volts   | 1        |

| 5.         | IC Base board         |                 | 1        |

| 6.         | Multimeter and probes |                 | 1 set    |

| 7.         | Connecting wires      |                 |          |

#### **PROCEDURE:**

- 1. The Wein bridge oscillator is designed for a given value of frequency (say 1 kHz) and the connections are made as shown in figure (1).

- 2. The dual power supply is verified to be  $\pm$ 15 V and then switched ON.

- 3. The feed-back resistor  $R_f$  is adjusted to get sustained oscillations.

- 4. The output waveform is observed on the CRO. The frequency and amplitude of oscillations are measured and recorded.

- 5. The measured frequency is compared with the designed frequency.

- 6. Steps 1-5 are repeated for different frequencies.

- 7. The above procedure is repeated for the RC Phase-shift oscillator circuit shown in figure (2).

# Circuit diagrams and designs:-

#### I. WEINBRIDGE OSCILLATOR:-

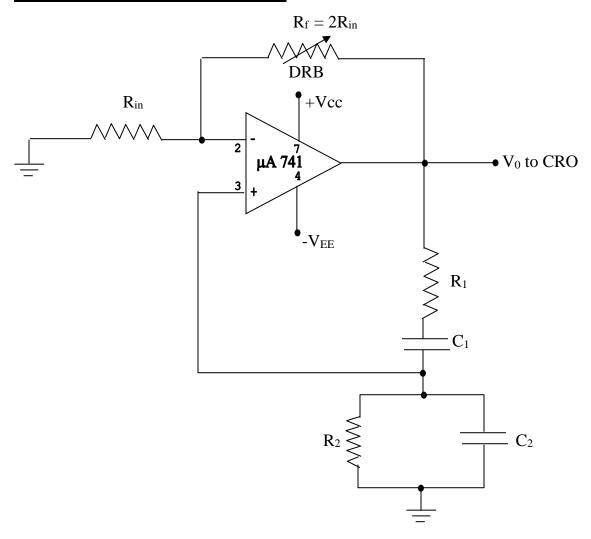

Fig (1): CIRCUIT DIAGRAM OF WEINBRIDGE OSCILLATOR

**DESIGN EXAMPLE:** The expression for frequency is:

$$f = \frac{1}{2\pi\sqrt{R_1R_2C_1C_2}} \qquad \text{Assuming} \quad R_1 = R_2 \qquad \& \quad C_1 = C_2 \,, \ \, \text{we have} \quad f = \frac{1}{2\pi RC}$$

Let f = 1 kHz.

Assume  $C = 0.1 \mu F$

$$f = \frac{1}{2\pi RC}$$

or  $R = \frac{1}{2\pi fc}$

:.

$$R = \frac{1}{2\pi \times 1K \times 0.1 \,\mu} = 1.591 \,\text{k}\Omega$$

$$R_{cal} = 1.59 \text{ k} \Omega$$

,

Use

$$R = 1.6 \text{ k}\Omega$$

# The condition for sustained oscillations is:

$$1 + \frac{R_f}{R_{in}} = 3$$

i.e.

$$\frac{R_f}{Rin} = 2$$

or  $R_f = 2 R_{in}$

Use  $R_{in} \!=\! 1~K~\Omega$  .  $~R_f = 2~K~\Omega$  [ Use a DRB and trim  $R_f$  to get sustained oscillations ]

#### **TABULAR COLUMN:-**

| Sl. | R | С  | $f_{cal}$ | T <sub>meas</sub> | $f_{ m meas}$ | V <sub>o</sub> (p-p)<br>Volts | $R_{\mathrm{f}}$ |

|-----|---|----|-----------|-------------------|---------------|-------------------------------|------------------|

| No. | Ω | μF | in Hz     | Msec              | Hz            | Volts                         | Ω                |

|     |   |    |           |                   |               |                               |                  |

|     |   |    |           |                   |               |                               |                  |

|     |   |    |           |                   |               |                               |                  |

|     |   |    |           |                   |               |                               |                  |

|     |   |    |           |                   |               |                               |                  |

|     |   |    |           |                   |               |                               |                  |

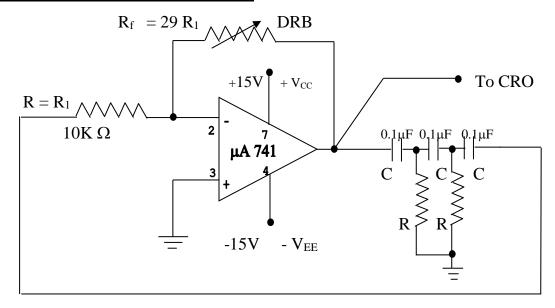

#### II. RC-PHASE SHIFT OSCILLATOR:-

Fig (2): CIRCUIT DIAGRAM OF RC-PHASE SHIFT OSCILLATOR

#### **DESIGN EXAMPLE :-** To design for a frequency of f = 1 KHz

The frequency of oscillations is given by  $f = \frac{1}{2\pi\sqrt{6}RC}$

Let f = 1 kHz. Assuming  $C = 0.1 \mu\text{F}$

$$f = \frac{1}{2\pi\sqrt{6}RC} \qquad ==> \qquad R = \frac{1}{2\pi\sqrt{6} f C}$$

R =

$$\frac{1}{2\pi\sqrt{6} \times 1 \text{K Hz} \times 0.1 \mu F}$$

= 649.747 Ω [ Use R = 660 Ω ]

The Necessary condition to get sustained oscillations is  $\frac{R_f}{R_1} = 29$

Therefore  $R_f = 29 R_1$

Assuming  $R_1$ ,  $R_f$  can be found [  $R_1 \ge 10 R$  ]

Let  $R_1$  = 10 K  $\Omega$  == >  $R_f$  = 290 K  $\Omega$

#### TABULAR COLUMN:-

| Sl.<br>No. | R<br>Ω | C<br>μF | f <sub>cal</sub><br>Hz | T <sub>meas</sub><br>m sec | f meas<br>Hz | V <sub>o</sub> (P-P)<br>volts | $R_{ m f} \Omega$ |

|------------|--------|---------|------------------------|----------------------------|--------------|-------------------------------|-------------------|

| 1          | 660    | 0.1     | 984                    |                            |              |                               |                   |

|            |        |         |                        |                            |              |                               |                   |

# **Experiment No. 5**

#### Date:

# ZCD AND VOLTAGE LEVEL DETECTORS.

AIM: To design and test the operation of ZCDs and voltage level detectors.

# APPARATUS REQUIRED:

| Sl.<br>No. | Particulars               | Range          | Quantity |

|------------|---------------------------|----------------|----------|

| 1.         | ΙC μΑ 741                 |                | 1        |

| 2.         | Power supply              | +15 v to -15 v | 1        |

| 3.         | ASG and probes            |                | 1 set    |

| 4.         | Adapters, CRO             |                | 3+1      |

| 5.         | Multimeter and Probes     |                | 1 set    |

| 6.         | IC base board, base board |                |          |

| 7.         | Connecting wires          |                |          |

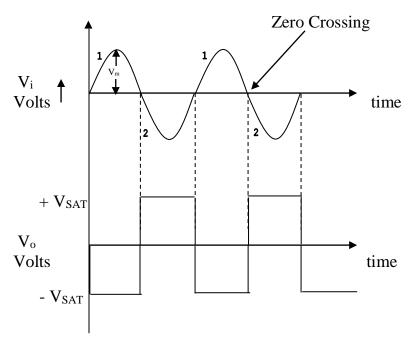

# **PROCEDURE:**

- 1. Circuit connections are made as shown in figure (1)

- 2. Sinusoidal input signal of is applied from an ASG.

- 3.  $V_{\text{o}}$  is observed on CRO . The Transfer characteristics is observed and the switching points at the Zero Crossing of the input are noted.

- 4. The circuit of figure (1) is modified to detect the input-crossing at specific positive and negative voltage levels == > Voltage Level detectors of figure (2) & (3) are tested.

# Circuit diagrams, Waveforms and Transfer Characteristics:-

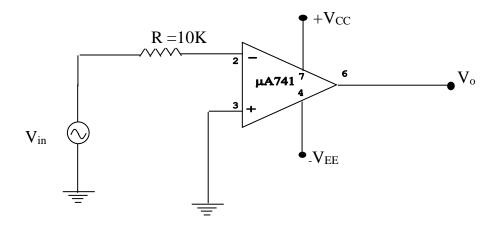

# (1) <u>ZCD</u>

Fig (1): ZCD CIRCUIT

Fig (1a): INPUT- OUTPUT WAVEFORMS of a ZCD

# (2) Positive Voltage Level Detector

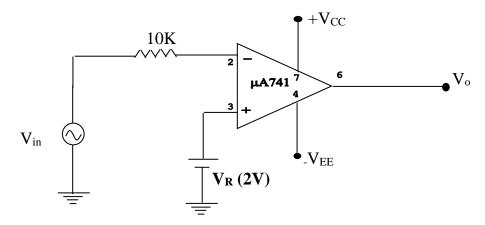

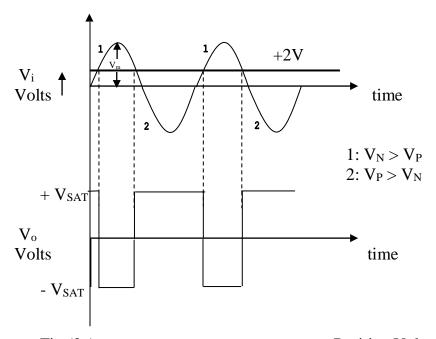

Fig (2): Positive Voltage Level Detector CIRCUIT

Fig (2a): INPUT- OUTPUT WAVEFORMS of a Positive Voltage Level Detector

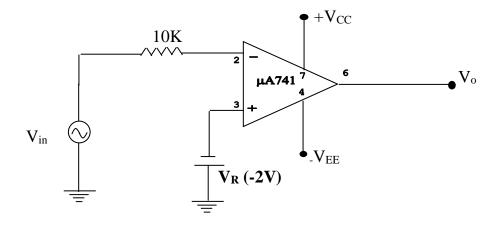

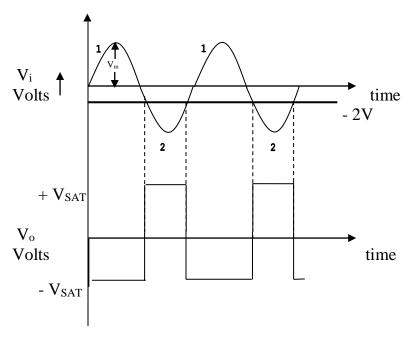

# (3) Negative Voltage Level Detector

Fig (3): Negative Voltage Level Detector CIRCUIT

Fig (3a): INPUT- OUTPUT WAVEFORMS of a Positive Voltage Level Detector

# Experiment No. 6

Date:-

# **SCHMITT TRIGGER CIRCUIT**

AIM: To design and test an inverting Schmitt trigger circuit for a given value of Hysterisis or UTP and LTP points.

#### APPARATUS REQUIRED:

| Sl.<br>No. | Particulars               | Range          | Quantity |

|------------|---------------------------|----------------|----------|

| 1.         | ΙC μΑ 741                 |                | 1        |

| 2.         | Resistors                 |                |          |

| 3.         | Power supply              | +15 v to -15 v | 1        |

| 4.         | ASG and probes            |                | 1 set    |

| 5.         | Adapters, CRO             |                | 3+1      |

| 6.         | Multimeter and Probes     |                | 1 set    |

| 7.         | IC base board, base board |                |          |

| 8.         | Connecting wires          |                |          |

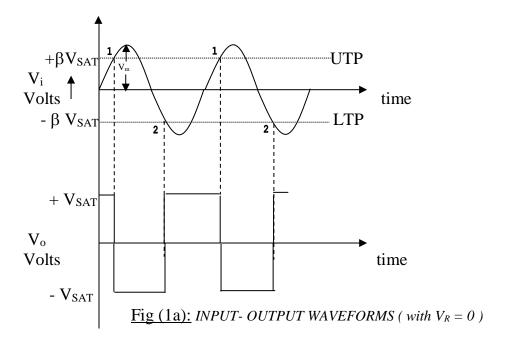

#### **PROCEDURE:**

- 1. Circuit connections are made as shown in figure (2)

- 2. Sinusoidal input signal of adequate amplitude ( more than the UTP & LTP values ) is applied from an ASG.

- 3.  $V_o$  is observed on CRO . The Transfer characteristics is observed and the switching points [ UTP & LTP ] are verified and noted.

- 4. The circuit is designed for a different value of hysterisis and tested.

# **Circuit diagrams, Waveforms and Transfer Characteristics:**

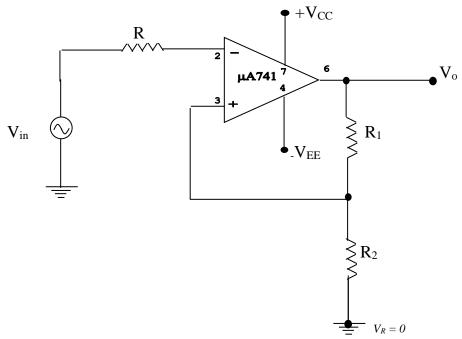

Fig (1):SCHMITT TRIGGER CIRCUIT

-----

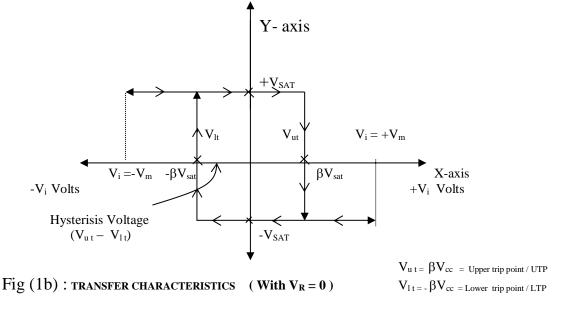

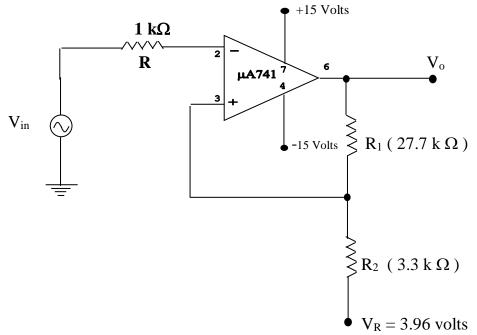

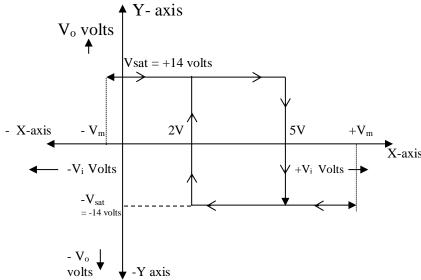

**Design Example :** To design a Schmitt trigger circuit using op-amp for an UTP of +5 volts and LTP of +2 volts . Assume  $+V_{SAT} = +14$  volts and  $-V_{SAT} = -14$  V.

Fig (2): Circuit diagram of Schmitt trigger for design example (1)

Fig (1b): TRANSFER CHARACTERISTICS (With  $+^{ve} V_R$ )

$$\begin{split} WKT: UTP &= \beta \ V_{SAT} \ + \ K \ V_{R} \ --- \ (1) \\ LTP &= - \beta V_{SAT} \ + \ K \ V_{R} \ --- \ (2) \\ \& V_{H} &= UTP - LTP --- \ (3) \end{split}$$

Given:  $V_H = 5 - 2 = 3$ <u>Step (1)</u> Eqn(1)-Eqn(2)= Eqn (3) y

Eqn(1)-Eqn(2)= Eqn (3) yields  $2 \beta V_{SAT} = 3$

$$\beta = \frac{3}{28} = 0.1071428$$

R<sub>2</sub>

or  $R_1 = 8.333 R_2$

for  $R_2 = 3.3 \text{ k }\Omega$ we get  $R_1 = 27.7 \text{ k }\Omega$  Step(2): To find  $V_R$ :

$$UTP = \beta V_{cc} + KV_{R}$$

i.e.  $\beta V_{SAT} = 1.5$

We can write  $5 = 1.5 + KV_R$

$$3.5 = \frac{R_1}{R_1 + R_2} V_R$$

$3.5 = 0.8935483 \text{ V}_{R}$

or

$$V_R = +3.92$$

volts

#### **Experiment No.7**

#### Date:

#### PRECISION HW & FW RECTIFIERS

Aim: To rig up and test Half wave and Full wave Precision Rectifiers.

Apparatus Required:

| Sl. | Apparatus        | Range                | Quantity |

|-----|------------------|----------------------|----------|

| No. |                  |                      |          |

| 1.  | ΙC μΑ 741        |                      | 2        |

| 2.  | Diodes           | BY 127               | 2        |

| 3.  | Resistors        | 10 k Ω               | 5        |

|     |                  | $1 \text{ k} \Omega$ | 2        |

| 4.  | Multi meter      |                      | 1        |

| 5.  | Adopters         |                      | 3        |

| 6.  | IC base board,   |                      | 1 set    |

|     | Base board       |                      |          |

| 7.  | ASG, Power       |                      | 1 set    |

|     | supply, CRO      |                      |          |

| 8.  | Connecting wires |                      | 1 set    |

#### **Procedure:**

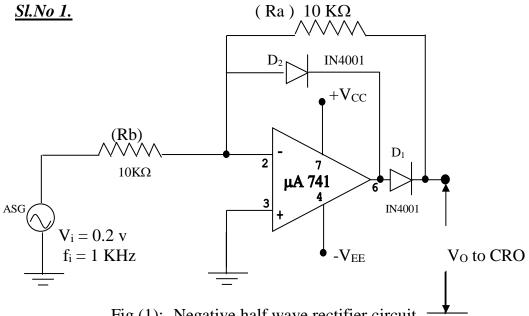

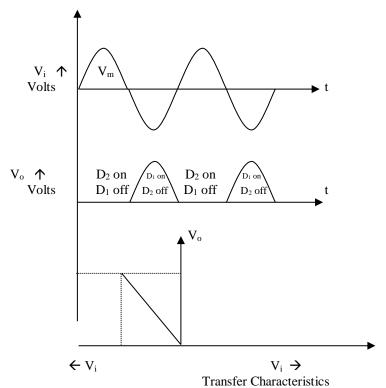

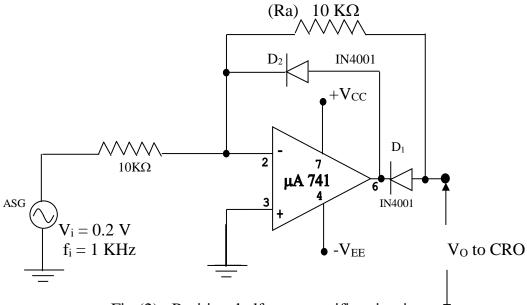

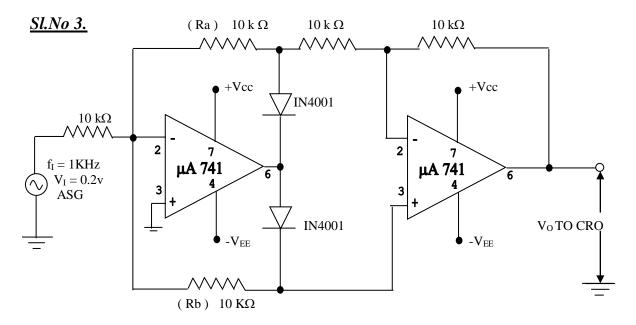

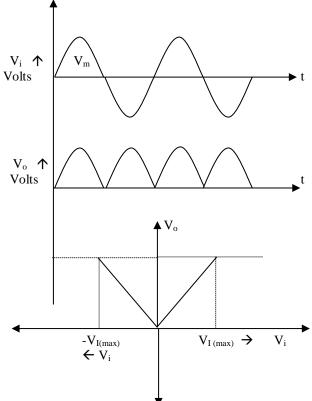

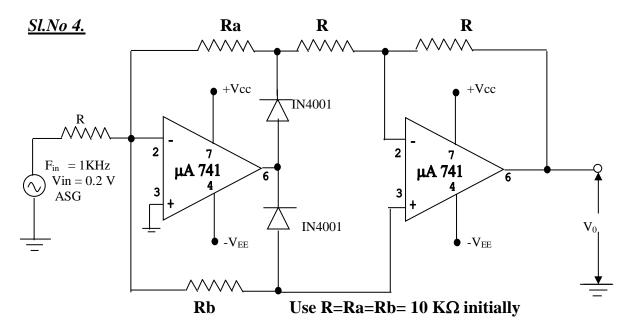

- 1) Connections are made as shown in the circuit of figure (1).

- 2) The bias supply is switched ON.

- 3) Sinusoidal input voltage of amplitude less than 0.7 V at a frequency of 1 kHz is applied and the output waveform is observed.

- 4) The input and output waveform are observed together on the CRO. The CRO is then set to X-Y mode and its transfer characteristic is observed.

- 5) The Values of Ra and / or Rb are changed and the change in the slope of the transfer curve is observed.

- 6) The above procedure is repeated for circuits of figure (2), (3) and (4).

# **Circuit Diagrams and Waveforms:-**

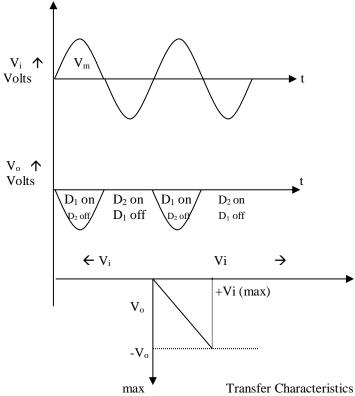

Fig (1):- Negative half wave rectifier circuit.

Fig (1a): WAVEFORMS & TRANSFER CURVE

# Sl.No 2.

Fig (2): Positive half wave rectifier circuit.

Fig (2a): WAVEFORMS & TRANSFER CURVE

Fig (3): Positive Full Wave Rectifier Circuit

Fig ( $^{\checkmark}$ 3a): WAVEFORMS & TRANSFER CURVE

Fig (4): Negative Full Wave Rectifier Circuit

Fig (4a): WAVEFORMS & TRANSFER CURVE

#### **Experiment No. 8**

Date:

#### FIRST AND SECOND ORDER ACTIVE LOW PASS FILTERS

AIM: To design and test I and II order ACTIVE LOW pass filters, and to obtain the frequency responses.

#### APPARATUS REQUIRED:

| Sl.<br>No. | Particulars           | Range   | Quantity |

|------------|-----------------------|---------|----------|

| 1.         | OP amp μA 741         |         |          |

| 2.         | Resistors             | 10 k Ω  | 3        |

| 3.         | Capacitors            | 0.01 μF | 2        |

| 4.         | ASG, CRO              |         |          |

| 5.         | Adopters              |         | 2        |

| 6.         | Power supply          | +/-15V  | 1        |

| 7.         | Multimeter and probes |         | 1+2 set  |

| 8.         | IC base board         |         | 1        |

| 0.         | base board            |         | 1        |

| 9.         | Connecting wires      |         |          |

#### **PROCEDURE:**

- 1. The first order LPF is designed for a given cut-off frequency  $f_h$ , say 5 KHz.

- 2. Connections are made as shown in figure(1) as per the design.

- 3. The input voltage is kept at a constant value (say 2 V) and the frequency is varied from 10 Hz to 100 KHz in steps, and at each step the output voltage is measured using a CRO and recorded.

- 4. The readings are tabulated and the gains in dB are calculated.

- 5. A graph of frequency Vs. gain in dB is plotted and the actual cut-off frequency  $(f_h)$  and the slope in the stop band (Roll-off rate) are determined from the graph plotted.

- 6. The above procedure is repeated for a II order LPF shown in figure (2).

# Circuit Diagrams, Ideal Graphs and Designs:-

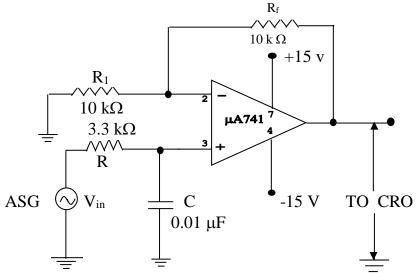

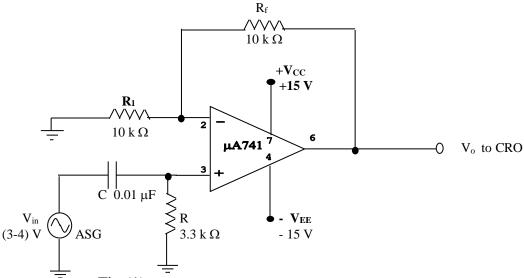

Fig (1): FIRST ORDER LOW PASS FILTER

# **Design Example:-**

Let the filter's PB gain  $A_f = 2$ Choose  $R_f = R_1 = 10 \text{ k} \Omega$

WKT,

$$f_h=\frac{1}{2\pi RC} \ . \ Given \quad f_h=5 \ KHz$$

$$If \ C=0.01 \ \mu F \quad then \ ., \qquad R=\frac{1}{2\pi \ x \ 0.01 \ \mu \ x \ 5k}=3.183 \ k \ \Omega \, .$$

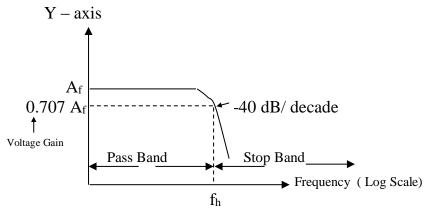

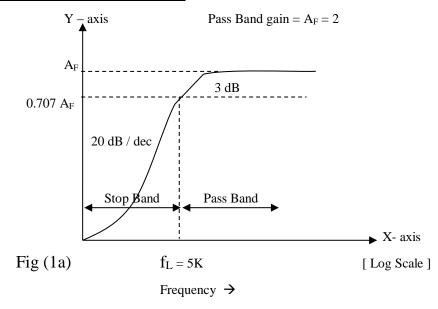

Fig (1a): Frequency response curve

# Tabular column :-

# $Constant \quad V_{in} = 2.0 \ volts$

| Sl.<br>No. | Frequency (Hz) | V <sub>o</sub> volts | $A_v = \frac{V_o}{V_i}$ | 20 logA <sub>v</sub><br>(Gain in dBs) |

|------------|----------------|----------------------|-------------------------|---------------------------------------|

|            |                |                      |                         |                                       |

|            |                |                      |                         |                                       |

|            |                |                      |                         |                                       |

|            |                |                      |                         |                                       |

|            |                |                      |                         |                                       |

|            |                |                      |                         |                                       |

|            |                |                      |                         |                                       |

-----

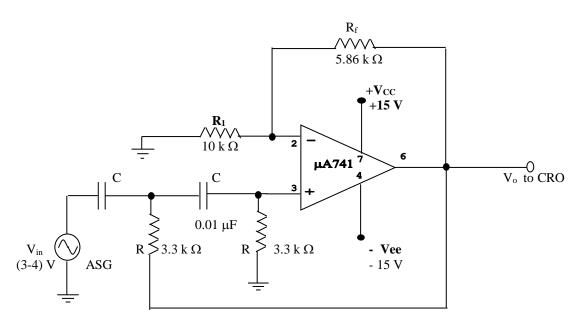

Fig (2): Circuit Diagram of Second order low pass filter

#### **Design Example:**

For Butterworth response (Flat Pass band),  $A_f = 1.586$

But

$$A_f = 1 + \frac{R_f}{R_1}$$

let  $\,R_1=10\;k\;\Omega\,$  , therefore  $R_f=5.80\;k\;\Omega\,$

Now

$$f_h = \frac{1}{2\pi\sqrt{R_2R_3C_2C_3}}$$

Assuming  $R_2 = R_3 = R$  and  $C_2 = C_3 = C$ ,

We have

$$f_h = \frac{1}{2\pi RC}$$

Given  $f_h = 5 \text{ kHz}$ .

Assuming  $C = 0.01 \mu F$ ,

$$R = \frac{1}{2\pi \times 0.01 \,\mu \times 5 \,k} = 3.183 \,K \qquad [Use \ 2.2 \,K + 1 \,K]$$

# Frequency response curve

Fig(2a): Frequency response curve

# **TABULAR COLUMN:-**

$\overline{Constant \ V_{in}} = 4 \ volts$

| Sl.<br>No. | Frequency (Hz) | V <sub>o</sub> volts | $A_v = \frac{V_o}{V_i}$ | 20 logA <sub>v</sub><br>(Gain in dBs) |

|------------|----------------|----------------------|-------------------------|---------------------------------------|

|            |                |                      |                         |                                       |

|            |                |                      |                         |                                       |

|            |                |                      |                         |                                       |

|            |                |                      |                         |                                       |

#### **Experiment No. 9**

Date:

## FIRST AND SECOND ORDER ACTIVE HIGH PASS FILTERS

AIM: To design and obtain the frequency responses of I and II order active high pass filters:

#### **APPARATUS REQUIRED:**

| Sl. | Particulars            | Range    | Quantity |

|-----|------------------------|----------|----------|

| No. |                        |          |          |

| 1.  | Op amp μA 741 IC       |          | 1        |

| 2.  | Resistors              |          |          |

| 3.  | Capacitors             | 0.01 μF  | 1        |

| 4.  | ASG, CRO               |          | 1        |

| 5.  | Adopters               |          | 2        |

| 6.  | Power supply           | +/- 15 V | 1        |

| 7.  | Multimeter with probes |          | 1+ 2 set |

| 8.  | Base board,            |          | 1 set    |

|     | IC Base board          |          |          |

| 9.  | Connecting wires       |          | 1 set    |

#### **PROCEDURE:**

- 7. The I order HPF is designed for a particular cut-off frequency ( $f_L$ ) (say 5 KHz) by choosing proper values of R and C.

- 8. Connections are made as shown in figure(1) as per the design.

- 9. The input voltage is kept at a constant value (say 2 V) and the frequency is varied from 10 Hz to 100 KHz in steps, and at each step the output voltage is measured using a CRO and recorded.

- 10. All the readings are tabulated and the gain in dB is calculated.

- 11. A graph of frequency Vs. gain in dB is plotted and the actual cut-off frequency  $(f_L)$  and the slope in the stop band are determined from the graph plotted.

- 12. The above procedure is repeated for the circuit of a II order HPF shown in figure (2).

#### CIRCUIT DIAGRAMS, DESIGNS AND FREQUENCY RESPONSES:-

Fig (1): CIRCUIT DIAGRAM OF I ORDER HIGH PASS FILTER

#### FREQUENCY RESPONSE:-

## **DESIGN EXAMPLE:-**

The cut-off frequency

$$f_L = \frac{1}{2\pi RC}$$

Let C = 0.01

$$\mu$$

F

$5 \text{ K} = \frac{1}{2\pi 0.01 \, \mu^* \, R}$  R = 3.18 k  $\Omega$  { Use 2.2K and 1K in series }

Use

$$R_1 = R_f = 10 \text{ k } \Omega$$

$\implies$   $A_F = 1 + \frac{R_f}{R_1}$   $\implies$  A gain of 2.

## **TABULAR COLUMN:-**

$\textit{CONSTANT} \ V_{in} = 4 \ volts$

| f in Hz | V o Volts | $A_{V} = \frac{V_{o}}{V_{i}}$ | A <sub>V</sub> in dB |

|---------|-----------|-------------------------------|----------------------|

|         |           |                               |                      |

|         |           |                               |                      |

|         |           |                               |                      |

|         |           |                               |                      |

|         |           |                               |                      |

|         |           |                               |                      |

|         |           |                               |                      |

\_\_\_\_\_\_

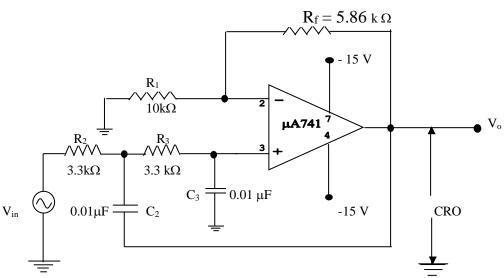

Fig (2):CIRCUIT DIAGRAM OF II ORDER HIGH PASS FILTER

#### **DESIGN EXAMPLE:-**

For the Circuit, PB gain is

$$A_F = 1 + \frac{R_f}{R_1}$$

For Butterworth response  $A_F=1.586$  Let  $R_1=10~k~\Omega,$

$$\begin{array}{ll} R_F = R_1 \, A_F - R_1 & = R_1 \, (\, 1.586 - 1) \\ & = 10 \, \, \text{K} \, x \, 0.586 = 5.86 \, k \, \Omega \\ \\ \text{for } f = 5 \, \text{kHz} & f_L = \frac{1}{2\pi \, \text{RC}} \\ \\ \text{Let C} = 0.01 \, \, \mu\text{F} & R = \frac{1}{2\pi \, x \, 5 \, k \, x \, 0.01 \, \mu} \\ \\ R = 3.18 \, k \, \Omega & \end{array}$$

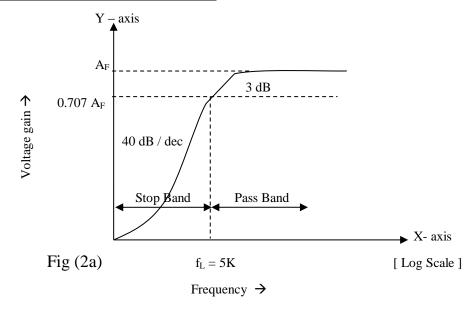

#### **FREQUENCY RESPONSE:-**

# TABULAR COLUMN:-

$\textit{CONSTANT} \quad V_{in} = 4 \ volts$

| f in Hz | V o Volts | $A_{V} = \frac{V_{o}}{V_{i}}$ | A <sub>V</sub> in dB |

|---------|-----------|-------------------------------|----------------------|

|         |           |                               |                      |

|         |           |                               |                      |

|         |           |                               |                      |

|         |           |                               |                      |

|         |           |                               |                      |

|         |           |                               |                      |

|         |           |                               |                      |

|         |           |                               |                      |

|         |           |                               |                      |

## Experiment No. 10

#### Date:

# ASTABLE & MONOSTABLE MULTIVIBRATORS USING 555 TIMER

AIM: To design and test Astable and Monostable Multivibrators for the given specifications using 555 timer IC.

## APPARATUS REQUIRED:

| Sl.<br>No. | Particulars           | Range           | Quantity |

|------------|-----------------------|-----------------|----------|

| 1.         | IC 555                |                 | 1        |

| 2.         | Diodes IN 4001        |                 | 2        |

| 3.         | Capacitor             | 0.1 and 0.01 μF | 1        |

| 4.         | DCB, ASG, Base board  |                 | 1        |

| 5.         | DRB                   |                 |          |

| 6.         | Resistors             |                 | 1        |

| 7.         | Power supply          | + 5 V           | 1        |

| 8.         | CRO and Probes        |                 | 1 set    |

| 9.         | Multimeter and probes |                 | 1 set    |

| 10.        | Adopters & wires      |                 | 3 sets   |

## **PROCEDURES:-**

## I. Astable Multivibrators (AMVs)

- 1. Connections are made as shown in the circuit of figure (1) and the power supply is switched ON.

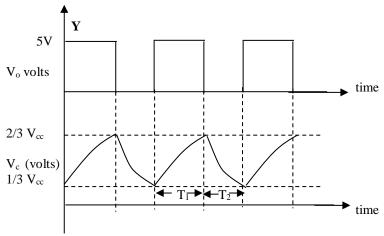

- 2. The output voltage waveform and the voltage across the timing capacitor are observed and traced using a CRO.

- 3. All the relevant voltage levels like 1/3 Vcc, 2/3 Vcc are noted.

Ton and Toff are also measured and noted. The frequency of oscillation and

the duty cycle are calculated and verified against the theoretical values.

5. The above procedure is repeated for different duty cycles as shown in circuits of figure (2) and (3).

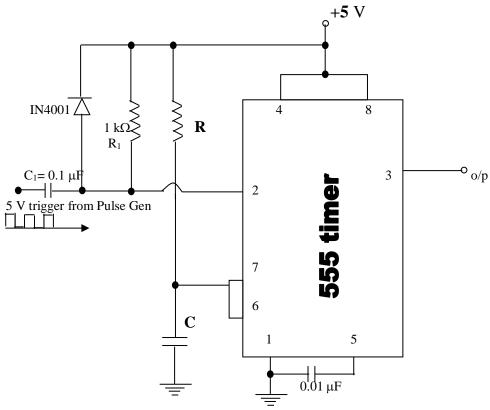

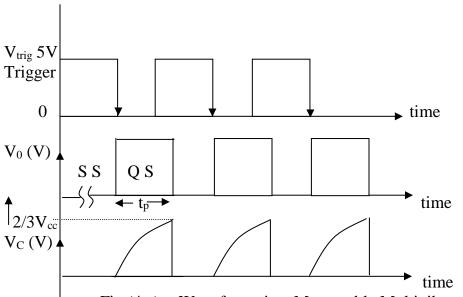

#### **II.** Monostable Multivibrator:-

- 1. The MMV is designed for a particular 'Pulse width' as per the design shown and the connections are made as shown in circuit of figure(4).

- 2. The input trigger signal's frequency and duty cycle are set to appropriate values and the output waveform is observed and verified for the required pulse width.

- The following combinations of waveforms are observed together on a CRO and traced.

a) Trigger signal and output signal

- b) Output waveform and Capacitor voltage

- 1) The pulse width is measured and noted

- 2) The above procedure is repeated for a different value of pulse width.

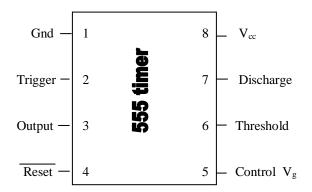

Fig (a): PIN DIAGRAM OF 555 timer

Note: In the circuit diagrams that follow, only pin numbers are marked. Referring to the pin diagram of Fig (a), specify the pin functions accordingly for all the circuit diagrams.

## Circuit Diagrams, Waveforms and Designs:-

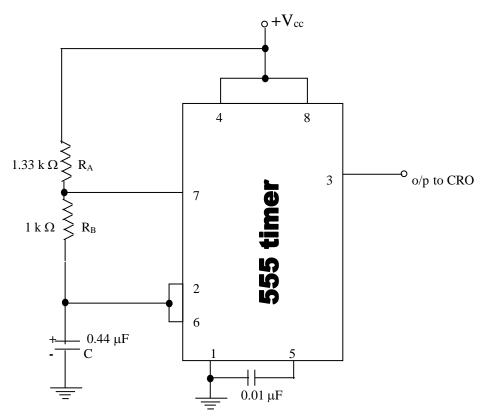

**Design Example 1:** To Design an Astable multivibrator circuit using 555 timer for f = 1 KHz, duty cycle = 70 % and  $V_{out} = 5$  Volts.

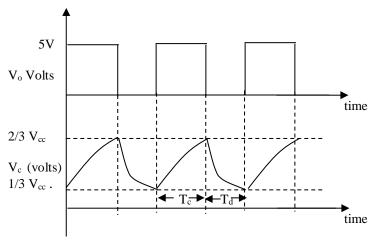

Fig (1): Circuit of Astable Multivibrator for duty cycle > 50 %

We Know that

$$\begin{split} T_1 &= 0.69 \ (\,R_A + R_B) \ C \quad \text{and} \quad T_2 \, = 0.69 \ R_B \, C \\ \text{and} \quad \text{Duty Cycle} &= \frac{T_1}{T_1 + T_2} = \frac{R_A + R_B}{R_A + 2R_B} \\ \text{Given duty cycle= } 70 \ \% \\ & \therefore \frac{R_A + R_B}{R_A + 2R_B} = \frac{70}{100} = 0.7 \\ \text{or} \quad R_A + R_B = 0.7 \ R_A + 1.4 \, R_B \\ 0.3 \, R_A &= 0.4 \ R_B \quad \text{or} \quad R_A = 1.33 \, R_B \\ \text{for} \quad R_B &= 1 \, k \, \Omega \quad , \quad R_A = 1.33 \, k \, \Omega \end{split}$$

$T = T_1 + T_2$  &  $T = 0.69 (R_A + 2R_B) C$

Given f = 1 KHz, therefore T = 1msec

$$1ms = 0.69 [ 1.33 K + ( 2 x 1 K ) ] x C$$

Therefore  $C = 0.44 \mu F$  (Use two numbers of 0.22  $\mu F$  in parallel)

Fig (1a): Waveforms in an Astable Multivibrator

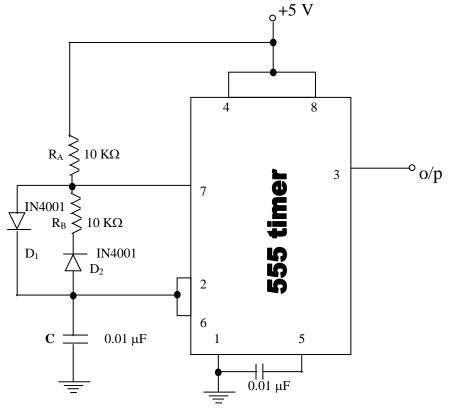

**Design Example 2 :** To design an astable multivibrator circuit using 555 timer for a frequency of 1 KHz, duty cycle =  $50 \% \& V_{out} = 5 Volts$ .

Fig (2): Circuit diagram of AMV for any duty cycle

**Fig(2a)**:

$$T_1 = 0.69 (R_A + R_{f1}) C$$

and  $T_2 = 0.69 (R_B + R_{f2}) C$

Assuming that the diodes' on- resistances  $R_{\rm fl}$  &  $R_{\rm f2}$  are same and neglecting

these, we get

$$T_1 = 0.69$$

(  $R_A$ ) C and  $T_2 = 0.69$  (  $R_B$ ) C

If

$$R_A = R_B = 10 \text{ k} \Omega$$

, then duty cycle =  $\{ R_A / (R_A + R_B) \} = 50 \%$

Given f = 1 kHz, and therefore T = 1ms. Further,  $T_1 = T_2 = 0.5$  msec

$$0.5 \text{ms} = 0.69 \text{ x } 10 \text{ k } \Omega \text{ x C}$$

$\rightarrow$   $C = 0.072 \text{ } \mu\text{F}$

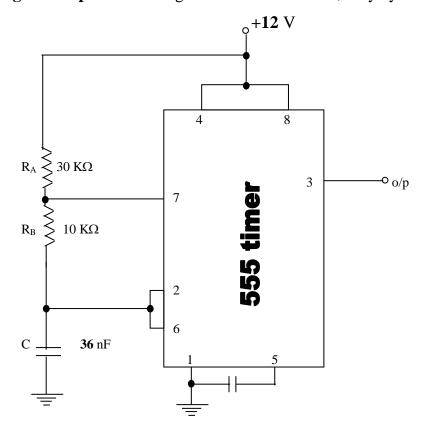

**Design Example 3:** To design an AMV for 1 KHz, duty cycle =  $0.8 \& V_{out} = 12 V$

Fig (3) 0.01 μF  $T_1 = 0.69$  (  $R_A + R_B$ ) C and  $T_2 = 0.69$   $R_B$  C Given., Duty cycle = 0.8 But Duty cycle =  $\frac{T_1}{T_1 + T_2} = \frac{R_A + R_B}{R_A + 2R_B} = 0.8$ ∴  $R_A + R_B = 0.8$   $R_A + 1.6$   $R_B$ or 0.2  $R_A = 0.6$   $R_B$ R A = 3  $R_B$ If  $R_B = 10$  K, then  $R_A = 30$  K

f = 0.69 (  $R_A + 2 R_B$ ) C given f = 1 kHz, T = 1ms Calculating., C = 36 nF.

\_\_\_\_\_

#### Monostable Multivibrator (MMV):-

Fig (4):- Monostable multivibrator circuit using 555 timer IC

Fig (4a):- Waveforms in a Monostable Multivibrator

**NOTE: -** SS: Stable State & QS: Quasi Stable State

**Design Example 1 :** To design a MMV for a pulse width of 1.25 msec Pulse width = 1.11 RC

$$RC = \frac{t_p}{1.11}$$

Let  $\,C=0.1~\mu F$  ;  $\,t_p=1.25~ms$

R =

$$\frac{1.25 \text{ ms}}{1.11 \text{x} \ 0.1 \ \mu}$$

= 11.267 k Ω [Use a 10 K and 1 K resistors in series.]

**Design Example 2:** To design a MMV for a pulse width of 3.0 msec

1) Let

$$C=0.1~\mu F$$

$$t_p=3ms$$

$$R=\frac{t_p}{1.11~x~C}$$

$$R=\frac{3~x~10^{-3}}{1.11~x~0.1~x~10^{-6}}=R=27.02~k\Omega~\text{ [Use }10~K+10~K+6.8~K~\text{in series ]}$$

#### Experiment No. 11

#### Date:

### DAC USING R-2R LADDER NETWORK

## Aim: To rig up and test a 4-bit R-2R ladder network DAC.

## **Apparatus Required:**

| S1. | <u>Particulars</u> | Range                  | Quantity |

|-----|--------------------|------------------------|----------|

| No. |                    |                        |          |

| 1   | μΑ741 IC           |                        | 1        |

| 2.  | Resistors          | <u>2.2 kΩ</u>          | 18       |

| 3.  | Power supply       | $\pm 15 \text{ volts}$ | 1        |

|     |                    | 0-5 volts              | 1        |

| 4.  | Multimeter and     | <u>-</u>               | 1 set    |

|     | <u>probes</u>      |                        |          |

| 5.  | Spring board,      | <u> </u>               | 1        |

|     | IC base board      |                        | 1 set    |

| 6.  | Connecting wires   | =                      | 1 set    |

#### **PROCEDURE:**

- 1) Connections are made as shown in fig (1).

- 2) The digital inputs  $b_1$ - $b_4$  are connected to a switch box. The 4 bits are increased in steps from 0000 to 1111 and at each step  $V_{out}$  is measured using a multimeter.

- 3) The readings are tabulated.

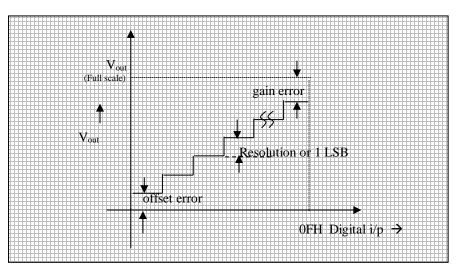

- 4) A graph of digital i/p versus analog o/p voltage is plotted, and the different parameters as shown in figure(2) are determined and recorded.

# Circuit Diagram:-

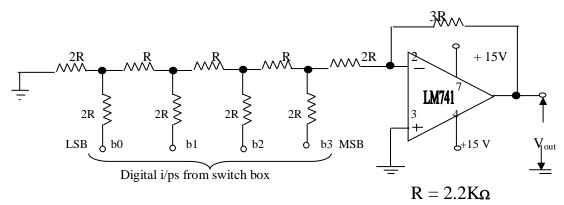

Fig(1): Circuit diagram of R-2R DAC

## **Design:**

$$V_{\text{out}} = -\frac{V_r}{2^n} \sum_{i=0}^{n-1} b_i 2^i$$

Where,  $b_i = 0 \text{ or } 1$

When all the digital i/p bits are 1 and  $V_{\rm r}$  = +5 volts.

## Tabular Column: -

| $b_3$ | $b_2$ | $b_1$ | $b_0$ | V <sub>out</sub> (Theoretical) volts | V <sub>out</sub> (Practical) Volts |

|-------|-------|-------|-------|--------------------------------------|------------------------------------|

| 0     | 0     | 0     | 0     |                                      |                                    |

| 0     | 0     | 0     | 1     |                                      |                                    |

| 0     | 0     | 1     | 0     |                                      |                                    |

| 0     | 1     | 1     | 1     |                                      |                                    |

| 0     | 1     | 0     | 0     |                                      |                                    |

51

| 0 | 1 | 0 | 1 |  |

|---|---|---|---|--|

| 0 | 1 | 1 | 0 |  |

|   |   | • |   |  |

|   |   | • | • |  |

| • | • | • | • |  |

| 1 | 1 | 1 | 1 |  |

| 1 | 1 |   |   |  |

## Typical Converter Relationship:-

Fig (2): Typical Converter Relationship

## **Results:-**

1) LSB or Resolution = \_\_\_\_\_ Volts

2) Offset error = \_\_\_\_\_ Volts

3)  $V_{out}$  (full scale) designed = \_\_\_\_\_ Volts

4)  $V_{out}$  (full scale) obtained = \_\_\_\_\_ Volts

5) Gain error = \_\_\_\_\_ Volts